50+ pages 16 to 1 multiplexer vhdl code 1.5mb. They provide 16 inputs 88. Generate RTL Schematic and simulate the 21 MUX using testbench. They provide 16 inputs 88. Read also code and learn more manual guide in 16 to 1 multiplexer vhdl code For Example if n 2 then the mux will be of 4 to 1 mux with 4 input 2 selection line and 1.

Hi this is a 8x1 mux. You can make 16x1 from it.

16 To 1 Mux Using 2 To 1 Mux In Vhdl Stack Overflow

| Title: 16 To 1 Mux Using 2 To 1 Mux In Vhdl Stack Overflow |

| Format: eBook |

| Number of Pages: 265 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: May 2021 |

| File Size: 2.1mb |

| Read 16 To 1 Mux Using 2 To 1 Mux In Vhdl Stack Overflow |

|

The middle level then groups the four outputs from the top level again into groups of two and selects one from each.

Architecture struct of 161mux is. First I wrote a 2 to 1 mux. Several different VHDL constructs can be used to define a multiplexer. Inpin std_logic_vector 7 downto 0. Multiplexers are used in communication systems to increase the amount of data that can be sent over a network within a certain. A 16 input multiplexer accepts 16 inputs i.

Multiplexers In Vhdl

| Title: Multiplexers In Vhdl |

| Format: PDF |

| Number of Pages: 338 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: June 2019 |

| File Size: 1.2mb |

| Read Multiplexers In Vhdl |

|

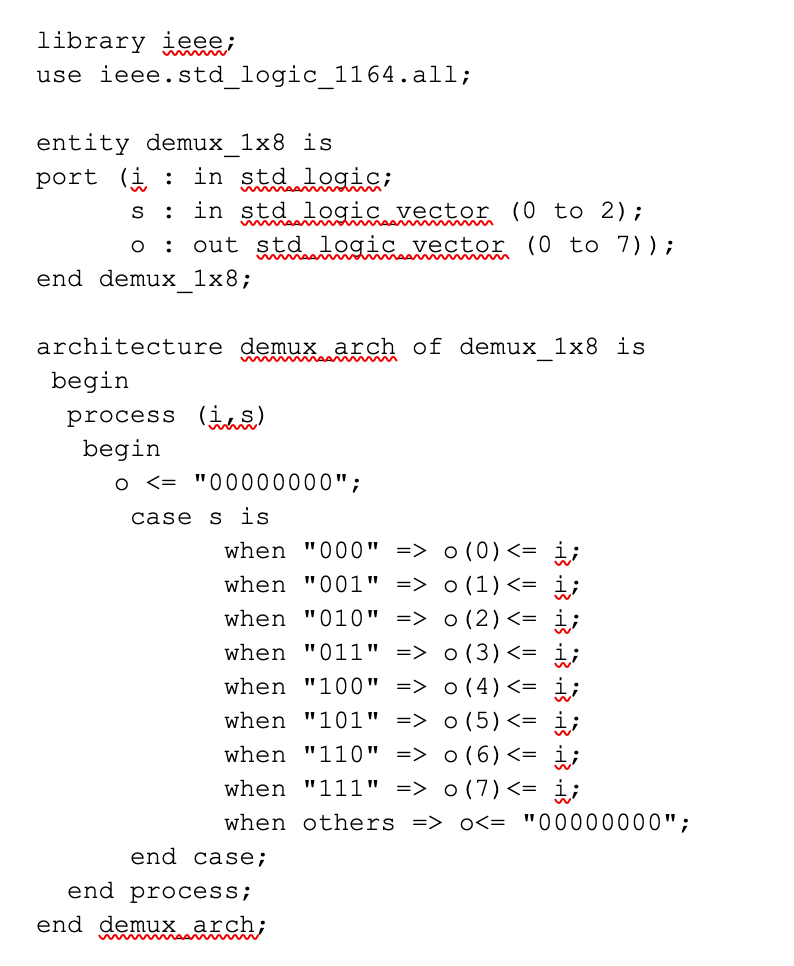

Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl

| Title: Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl |

| Format: eBook |

| Number of Pages: 349 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: November 2018 |

| File Size: 2.8mb |

| Read Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl |

|

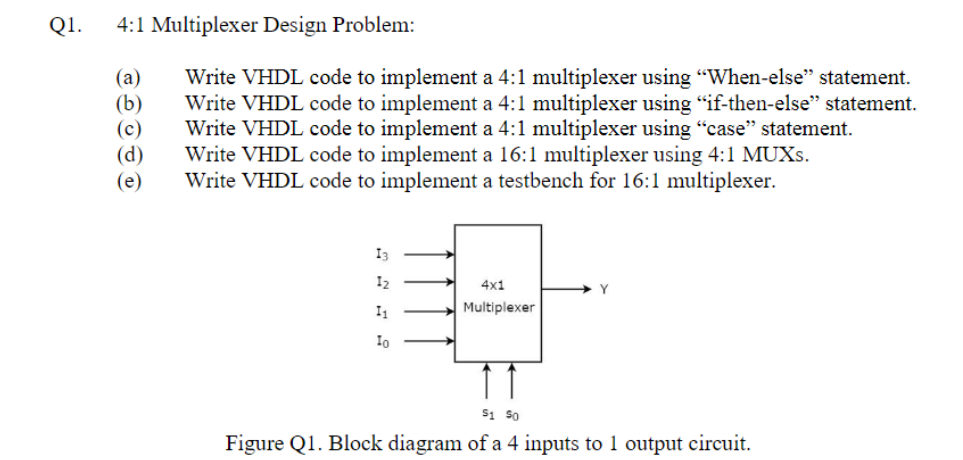

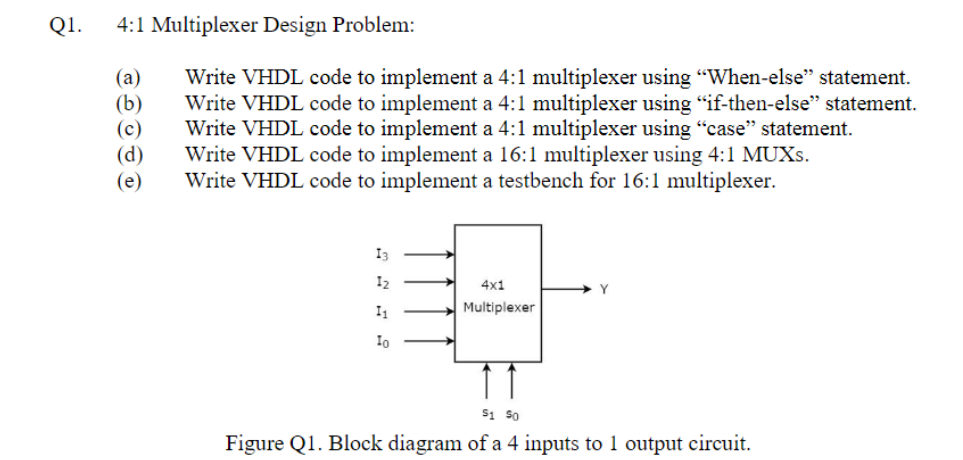

4 1 Multiplexer Design Problem A B C Write Vhdl Chegg

| Title: 4 1 Multiplexer Design Problem A B C Write Vhdl Chegg |

| Format: ePub Book |

| Number of Pages: 336 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: August 2020 |

| File Size: 2.6mb |

| Read 4 1 Multiplexer Design Problem A B C Write Vhdl Chegg |

|

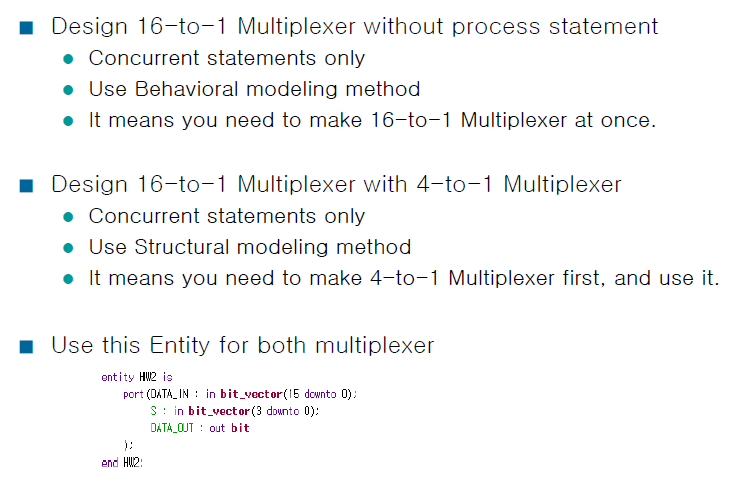

Design 16 To 1 Multiplexer Without Process Statement Chegg

| Title: Design 16 To 1 Multiplexer Without Process Statement Chegg |

| Format: eBook |

| Number of Pages: 139 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: June 2019 |

| File Size: 2.3mb |

| Read Design 16 To 1 Multiplexer Without Process Statement Chegg |

|

Multiplexer Handling 16 Bits Electrical Engineering Stack Exchange

| Title: Multiplexer Handling 16 Bits Electrical Engineering Stack Exchange |

| Format: ePub Book |

| Number of Pages: 334 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: February 2019 |

| File Size: 1.1mb |

| Read Multiplexer Handling 16 Bits Electrical Engineering Stack Exchange |

|

On A Low Pass Fir Filter For Ecg Denoising In Vhdld An Cn Th

| Title: On A Low Pass Fir Filter For Ecg Denoising In Vhdld An Cn Th |

| Format: eBook |

| Number of Pages: 256 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: June 2020 |

| File Size: 800kb |

| Read On A Low Pass Fir Filter For Ecg Denoising In Vhdld An Cn Th |

|

Code For 16 1 Mux Using For Generate

| Title: Code For 16 1 Mux Using For Generate |

| Format: eBook |

| Number of Pages: 235 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: August 2018 |

| File Size: 1.3mb |

| Read Code For 16 1 Mux Using For Generate |

|

Design 16 To 1 Multiplexer Without Process Statement Chegg

| Title: Design 16 To 1 Multiplexer Without Process Statement Chegg |

| Format: ePub Book |

| Number of Pages: 155 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: January 2021 |

| File Size: 800kb |

| Read Design 16 To 1 Multiplexer Without Process Statement Chegg |

|

Vhdl Code For A Parator Full Vhdl Code Together With Testbench For The Parator Are Provided Coding Chart Projects

| Title: Vhdl Code For A Parator Full Vhdl Code Together With Testbench For The Parator Are Provided Coding Chart Projects |

| Format: ePub Book |

| Number of Pages: 163 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: May 2018 |

| File Size: 1.5mb |

| Read Vhdl Code For A Parator Full Vhdl Code Together With Testbench For The Parator Are Provided Coding Chart Projects |

|

16 Bit Cpu Design In Logisim Fpga4student 16 Bit Circuit Diagram Design

| Title: 16 Bit Cpu Design In Logisim Fpga4student 16 Bit Circuit Diagram Design |

| Format: PDF |

| Number of Pages: 181 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: April 2017 |

| File Size: 1.3mb |

| Read 16 Bit Cpu Design In Logisim Fpga4student 16 Bit Circuit Diagram Design |

|

21 Write The Plete Vhdl Code For A 16 To 1 Chegg

| Title: 21 Write The Plete Vhdl Code For A 16 To 1 Chegg |

| Format: eBook |

| Number of Pages: 251 pages 16 To 1 Multiplexer Vhdl Code |

| Publication Date: December 2018 |

| File Size: 1.4mb |

| Read 21 Write The Plete Vhdl Code For A 16 To 1 Chegg |

|

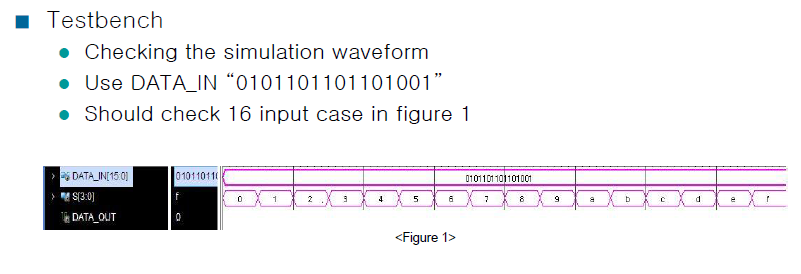

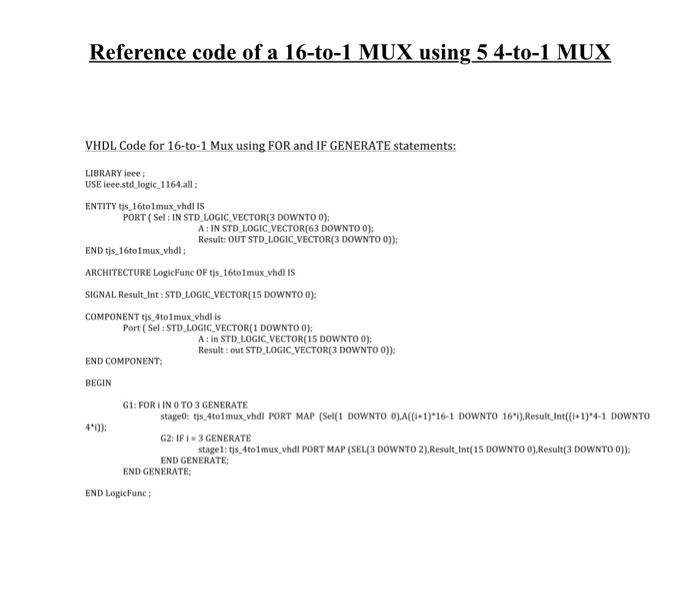

Several different VHDL constructs can be used to define a multiplexer. I actually thought that to do this we may need 15 two to one multiplexers and by wiring them together and using structural model I wrote the code below. What is a multiplexer.

Here is all you have to to learn about 16 to 1 multiplexer vhdl code Sin bit_vector 0 to 3. The input data lines are controlled by n selection lines. We can use concurrent signal assignment statement a selected signal assignment statement. Multiplexer handling 16 bits electrical engineering stack exchange 16 bit cpu design in logisim fpga4student 16 bit circuit diagram design 4 1 multiplexer design problem a b c write vhdl chegg multiplexers in vhdl vhdl tutorial 14 design 1 8 demultiplexer and 8 1 multiplexer using vhdl vhdl code for a parator full vhdl code together with testbench for the parator are provided coding chart projects 24 and requires 4 selection lines.

0 Comments